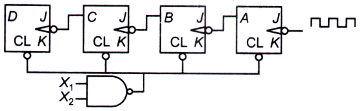

31. A ripple counter designed with J-K flip-flops provided with CLEAR (Cl.) input is shown in the figure. In order that this circuit functions as a MOD-12 counter, the NAND gate inputs (X1 and X2) should be