A common emitter transistor amplifier circuit is operated under a fixed bias. In this circuit, the operating point

A. remains fixed with an increase in temperature

B. moves towards cut-off region with an increase in temperature

C. moves towards the saturation region with a decrease in temperature

D. moves towards the saturation region with an increase in temperature

Answer: Option D

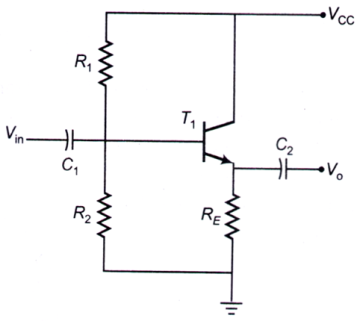

A. is a common-emitter amplifier

B. uses a p-n-p transistor

C. is an oscillator

D. has a voltage gain less than one

A. 1 AND gate

B. 2 AND gates

C. 1 OR gate

D. 2 OR gates

A. the gain decreases by 10 times

B. the output resistance increases by 10 times

C. the fH increases by 100 times

D. the input resistance decreases by 100 times

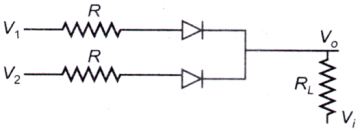

The following circuit (where, RL ≫ R) performs the operation of

A. OR gate for a negative logic system

B. NAND gate for a negative logic system

C. AND gate for a positive logic system

D. AND gate for a negative logic system

Join The Discussion