1. A 5 bit DAC has a current output. For a digital input of 10100, an output current of 10 mA is produced. What will be the output current for a digital input of 11101?

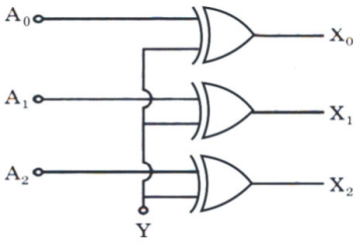

2. In the figure shown, X2X1X0 will be 1's complement of A2A1A0 if

$${\overline {\text{A}} _0} = {\overline {\text{A}} _1} = {\overline {\text{A}} _2}$$

$${\overline {\text{A}} _0} = {\overline {\text{A}} _1} = {\overline {\text{A}} _2}$$

3. A standard CMOS inverter is designed with equal rise and fall times (βn = βp). If the width of the PMOS transistor in the inverter is increased, what would be the effect on the LOW noise margin (NML) and the HIGH noise margin NMH ?

4. A divide-by-78 counter can be realized by using

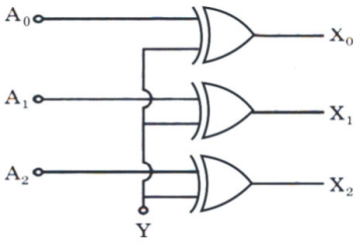

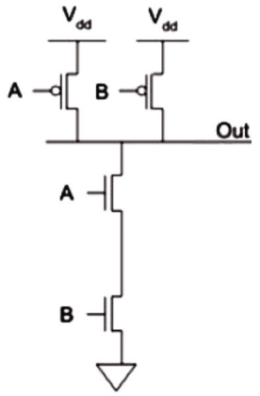

5. The circuit shown in the following figure is a . . . . . . . . gate.

6. A 10 bit ADC has a range of ±5 V. The resolution of the ADC is approximately

7. A dynamic RAM consists of

8. Considering signed-magnitude representation for negative numbers, -42 will be stored into an 8-bit memory space as

9. The decoding error of the counter can be avoided by

10. The current mode logic (CML) is same as

Read More Section(Digital Electronics)

Each Section contains maximum 100 MCQs question on Digital Electronics. To get more questions visit other sections.